# LSU Digital Commons

LSU Doctoral Dissertations

Graduate School

2010

## Carbon Nanotube Interconnect Modeling for Very Large Scale Integrated Circuits

Yao Xu

Louisiana State University and Agricultural and Mechanical College

Follow this and additional works at: https://digitalcommons.lsu.edu/gradschool\_dissertations

Part of the <u>Electrical and Computer Engineering Commons</u>

#### Recommended Citation

Xu, Yao, "Carbon Nanotube Interconnect Modeling for Very Large Scale Integrated Circuits" (2010). LSU Doctoral Dissertations. 3778. https://digitalcommons.lsu.edu/gradschool\_dissertations/3778

This Dissertation is brought to you for free and open access by the Graduate School at LSU Digital Commons. It has been accepted for inclusion in LSU Doctoral Dissertations by an authorized graduate school editor of LSU Digital Commons. For more information, please contactgradetd@lsu.edu.

## CARBON NANOTUBE INTERCONNECT MODELING FOR VERY LARGE SCALE INTERGRATED CIRCUITS

#### A Dissertation

Submitted to the Graduate Faculty of the Louisiana State University and Agricultural and Mechanical College in Partial fulfillment of the requirements for the degree of Doctor of Philosophy

in

The Department of Electrical and Computer Engineering

by

Yao Xu B.S., Tsinghua University, Beijing, China July, 2000 M.S., Louisiana State University, Baton Rouge, LA 70803, USA May, 2011

To my loving and supportive wife, Xiuli

&

To my wonderful sons, Evan & Kevin

#### **ACKOWLEDGMENTS**

My thanks and special appreciation to my advisor and mentor Dr. Ashok Srivastava. I am very thankful for his guidance, patience and understanding throughout my dissertation research. I would have not completed this research without his suggestions, discussions and constant encouragement.

I would like to thank Committee members Late Dr. Jorge L. Aravena, Dr. Tryfon T. Charalampopoulos, Dr. Jin-Woo Choi, Dr. Theda Daniels-Race, Dr. Jonathan P. Dowling, Dr. Martin Feldman, Dr. Suresh Rai and Dr. R. Vaidyanathan for being a part of my committee.

I am thankful to Dr. Ashwani K. Sharma of US Air Force Research Laboratory, Kirtland Air Force Base, New Mexico, for his support and encouragement for the research carried out in this project.

Above all, I am deeply grateful to my fellow co-workers, Chen Fang, Yang Liu, Chunbo Ni, Dr. Jose Mauricio Marulanda Prado, Wei Shu, Rajiv Soundararajan, Juyu Wang and Dr. Siva Yellampalli.

## **TABLE OF CONTENTS**

| ACKNOWLE     | DGMENTS                                               | iii  |

|--------------|-------------------------------------------------------|------|

| LIST OF TAB  | LES                                                   | vi   |

| LIST OF FIGU | JRES                                                  | vii  |

| ABSTRACT     |                                                       | xiii |

| CHAPTER 1    | INTRODUCTION                                          | 1    |

| 1.1          | Challenges of Silicon Integrated Circuits             | 1    |

| 1.2          | Introduction to Carbon Nanotubes                      |      |

| 1.3          | Structure of Carbon Nanotubes                         | 2    |

| 1.4          | Properties of Single-Walled Carbon Nanotubes          | 5    |

|              | 1.4.1 Electronic Band Structure                       |      |

|              | 1.4.2 Density of States                               |      |

| 1.5          | Applications of CNTs in Integrated Circuits           |      |

|              | 1.5.1 Applications of Semiconducting Carbon Nanotubes |      |

|              | 1.5.2 Applications of Metallic Carbon Nanotubes       |      |

| 1.6          | Synthesis of Carbon Nanotubes                         |      |

| 1.7          | CNT Based Circuit Modeling                            | 18   |

|              | 1.7.1 CNT-FET Modeling                                |      |

|              | 1.7.2 CNT Interconnect Modeling                       |      |

| 1.8          | Scope of Research                                     | 19   |

| CHAPTER 2    | CARBON NANOTUBE FIELD-EFFECT TRANSISTOR               | 21   |

| 2.1          | Background of CNT-FETs                                | 21   |

| 2.2          | Surface Potential of CNT-FETs                         |      |

| 2.3          | Non-Ballistic CNT-FET Modeling                        | 36   |

|              | 2.3.1 Current Transport Modeling                      |      |

|              | 2.3.2 Logic Gates Modeling                            |      |

|              | 2.3.3 Dynamic Modeling                                | 42   |

| 2.4          | Ballistic CNT-FET Modeling                            |      |

| 2.5          | Verilog-AMS Simulations                               |      |

| 2.6          | Summary                                               | 53   |

| CHAPTER 3    | MODELING SINGLE-WALLED CARBON NANOTUBE                |      |

|              | INTERCONNECTION FOR VLSI                              | 59   |

| 3.1          | Introduction to Carbon Nanotube Interconnection       | 59   |

| 3.2          | Two-Dimensional Fluid Model                           | 61   |

| 3.3          | One-Dimensional Fluid Model                           | 65   |

| 3.4          | Transmission Line Model                               | 71   |

| 3.5          | Results and Discussion                                | 73   |

| 3.6          | Summary                                               | 85   |

| CHAPTER 4  | MODELING MULTI-WALLED AND BUNDLE OF SINGLE-WALLED CARBON NANOTUBES INTERCONNECTION FOR |     |

|------------|----------------------------------------------------------------------------------------|-----|

|            | VLSI                                                                                   | 88  |

| 4.1        | MWCNT Interconnection Modeling                                                         |     |

| 4.2        | SWCNT Bundle Interconnection Modeling                                                  | 91  |

| 4.3        | Performance of MWCNT and Bundles of SWCNT Interconnects                                |     |

| 4.4        | Summary                                                                                | 110 |

| CHAPTER 5  | CARBON NANOTUBE WIRE INDUCTOR                                                          | 111 |

| 5.1        | On-Chip Inductor Modeling                                                              | 112 |

| 5.2        | LC Voltage-Controlled Oscillator (VCO)                                                 | 114 |

| 5.3        | Summary                                                                                | 122 |

| CHAPTER 6  | ENERGY RECOVERY TECHNIQUES                                                             | 123 |

| 6.1        | Energy Recovery Logic (ERL)                                                            | 124 |

|            | 6.1.1 2N-2N2P Logic                                                                    | 124 |

|            | 6.1.2 Quasi-Static Energy Recovery Logic (QSERL)                                       | 126 |

|            | 6.1.3 Clocked Adiabatic Logic (CAL)                                                    |     |

|            | 6.1.4 New CAL XNOR/XOR Gate                                                            |     |

|            | 6.1.5 Simulation Results                                                               | 131 |

|            | 6.1.6 Experimental Results                                                             | 135 |

| 6.2        | CNT-FET Energy Recovery Circuits                                                       | 135 |

| 6.3        | Summary                                                                                | 140 |

| CHAPTER 7  | FAULT MODELING IN CNT BASED DIGITAL CIRCUITS                                           |     |

| 7.1        | CNT-FET Logic Gates                                                                    | 141 |

| 7.2        | Fault Models                                                                           | 144 |

|            | 7.2.1 Stuck-At Fault Model                                                             |     |

|            | 7.2.2 Stuck-Open Fault Model                                                           |     |

|            | 7.2.3 Stuck-On Fault Model                                                             |     |

| 7.3        | Summary                                                                                | 146 |

| CHAPTER 8  | CONCLUSION AND SCOPE OF FUTURE WORK                                                    |     |

| 8.1        | Conclusion                                                                             |     |

| 8.2        | Scope of Future Work                                                                   | 151 |

| REFERENCES | · · · · · · · · · · · · · · · · · · ·                                                  | 153 |

| APPENDIX A | VERILOG-AMS CODES FOR NONBALLISTIC CNT-FET MODELING                                    | 173 |

| APPENDIX B | CARBON NANOTUBE FOR BIO- AND CHEMICAL SENSING                                          | 180 |

| APPENDIX C | EXPERIMENTAL CHARACTERIZATION OF CNT INTERCONNECTS                                     | 182 |

| X ZITT A   |                                                                                        | 101 |

## LIST OF TABLES

| Table 1.1: | Mechanical properties of carbon nanotubes and comparison with other materials [27]     | 4   |

|------------|----------------------------------------------------------------------------------------|-----|

| Table 1.2: | Electrical properties of carbon nanotubes and comparison with other materials [28, 29] | 4   |

| Table 4.1: | A comparison of calculated and measured resistances of MWCNT interconnects             | 100 |

| Table 4.2: | A comparison of MWCNT interconnect model parameters                                    | 100 |

| Table 4.3: | Power dissipation ratio of MWCNT and SWCNT bundle to Cu interconnects                  | 109 |

## LIST OF FIGURES

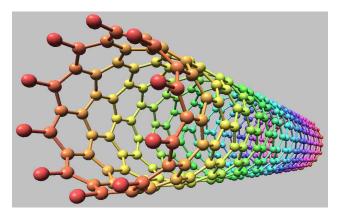

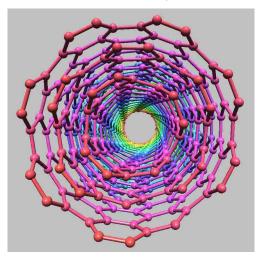

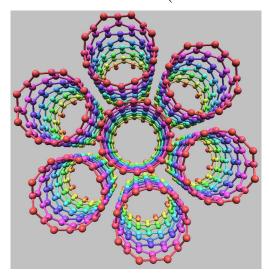

| Figure 1.1: | Single-walled carbon nanotube (Nanotube Modeler Software) [26]                                                                                                                                                                                                   | 3  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2: | Multi-walled carbon nanotubes (Nanotube Modeler Software) [26]                                                                                                                                                                                                   | 3  |

| Figure 1.3: | Single-walled carbon nanotubes bundle (Nanotube Modeler Software) [26].                                                                                                                                                                                          | 3  |

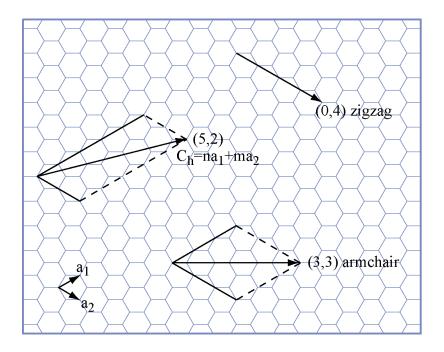

| Figure 1.4: | Schematic representation of a chiral vector in the crystal lattice of a carbon nanotube.                                                                                                                                                                         | 7  |

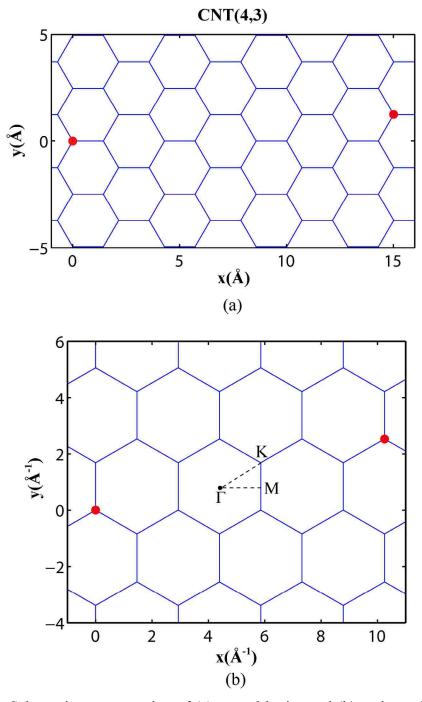

| Figure 1.5: | Schematic representation of (a) crystal lattice and (b) reciprocal lattice of a carbon nanotube with chiral vector (4,3).                                                                                                                                        | 9  |

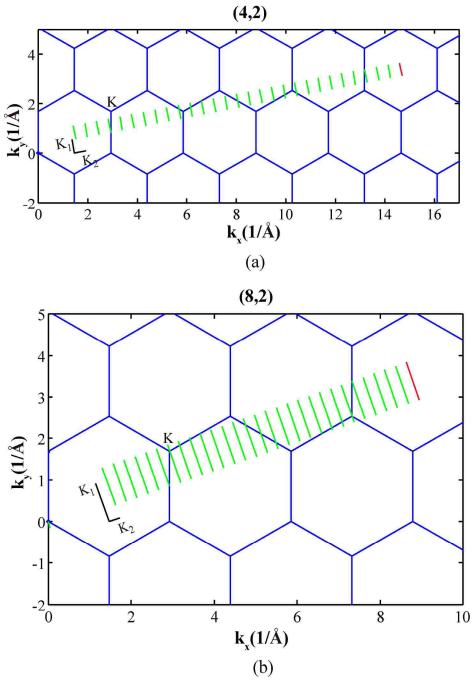

| Figure 1.6: | Plot of the allowed wave vectors in k-space for a CNT with (a) chiral vector (4,2) and (b) chiral vector (8,2)                                                                                                                                                   | 11 |

| Figure 1.7: | Plot of the energy band diagram in k-space for a CNT with (a) chiral vector (4,2) and (b) chiral vector (8,2). <b>Note</b> : Bang gap is the distance between the top of the valence band and the bottom of the conduction band marked by 1 in (a)               | 12 |

| Figure 1.8: | Plot of the density of states for a CNT with (a) chiral vector (4,2) and (b) chiral vector (8,2).                                                                                                                                                                | 13 |

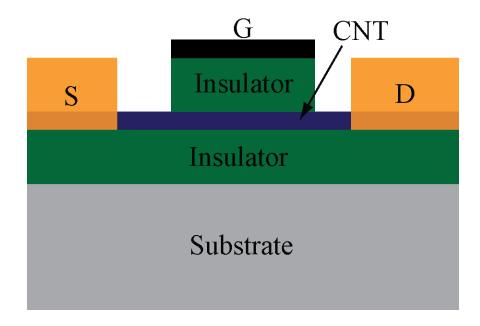

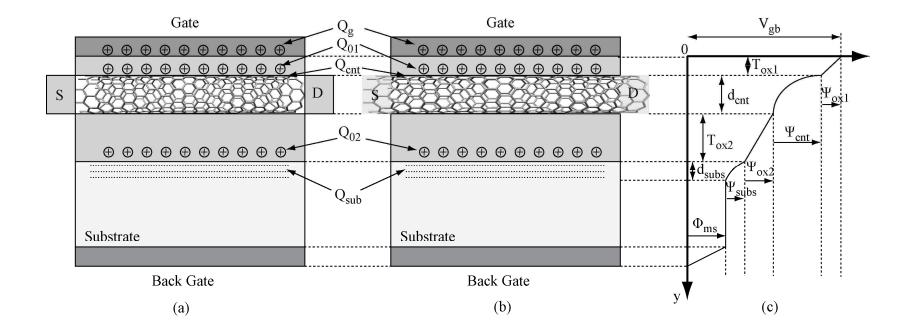

| Figure 2.1: | Typical vertical cross-section of a CNT-FET. <b>Note</b> : Insulators in the figure are SiO <sub>2</sub> or high-κ dielectric                                                                                                                                    | 24 |

| Figure 2.2: | (a) Plot of the charges from the gate to the substrate for Schottky Barrier CNT-FET, (b) Plot of the charges from the gate to the substrate for MOSFET-like CNT-FET and (c) plot of the potential distribution from the gate to the substrate in a CNT-FET [91]. | 26 |

| Figure 2.3: | Energy band diagram of a two terminal CNT-FET for (a) $V_{gb} = V_{fb}$ and (b) $V_{gb} > 0$ . Note: HfO <sub>2</sub> is the high- $\kappa$ dielectric hafnium oxide [91].                                                                                       | 32 |

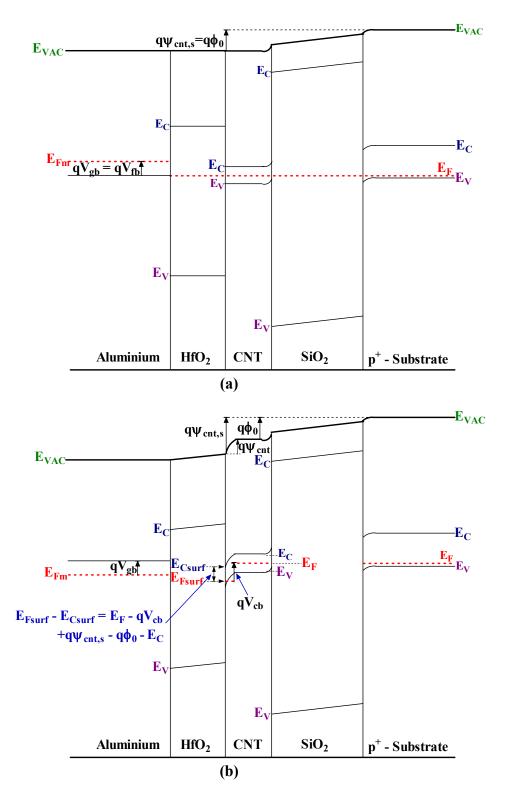

| Figure 2.4: | I-V characteristics of CNT-FET (11,9) with $V_{fb}$ = -0.79 V and $\phi_0$ = 0. The device dimensions are $T_{ox1}$ = 15 nm, $T_{ox2}$ = 120 nm and L = 250 nm. In modeled curve, $Q_{01}$ = $Q_{02}$ = 0 and $\lambda$ = 0.1 V <sup>-1</sup>                    | 38 |

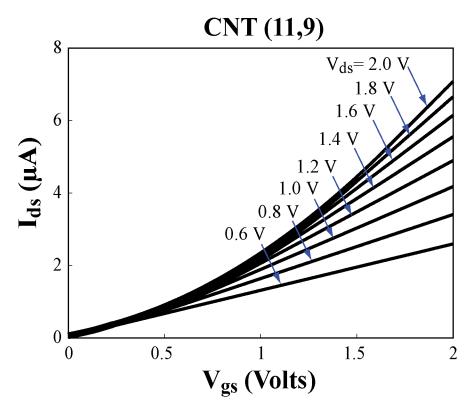

| Figure 2.5: Current, $I_{ds}$ versus gate to source voltage, $V_{gs}$ using $V_{fb}$ = -0.79 and $\varphi_0$ =0 for CNT-FET (11,9). The device dimensions are: $T_{ox1}$ = 15 nm, $T_{ox2}$ = 120 nm and $L$ = 250 nm. In modeled curve, $Q_{01}$ = $Q_{02}$ = 0 and $\lambda$ = 0.1 $V^{-1}$ |                                                                                                                                                                                                                                                                                                                                         |    |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

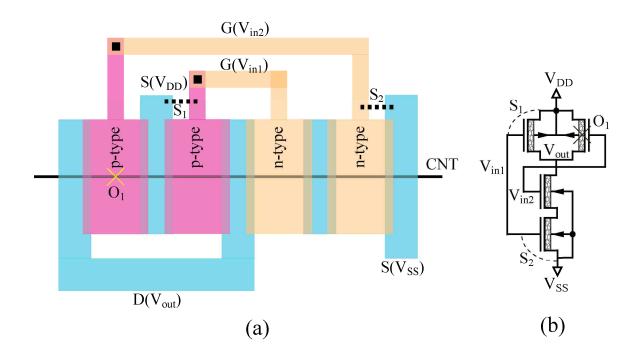

| Figure 2.6:                                                                                                                                                                                                                                                                                   | CNT-FET logic: (a) Inverter, (b) two input NAND gate and (c) two input NOR gate                                                                                                                                                                                                                                                         | 40 |  |

| Figure 2.7:                                                                                                                                                                                                                                                                                   | Voltage transfer characteristics of an inverter using CNT-FETs (11,9) with $V_{fb}=0$ V, $\lambda=0$ , 0.1 V <sup>-1</sup> and $\varphi_0=0$ . The dimensions of both the n-type CNT-FET and p-type CNT-FET are: $T_{ox1}=15$ nm, $T_{ox2}=120$ nm and $L=250$ nm                                                                       | 41 |  |

| Figure 2.8:                                                                                                                                                                                                                                                                                   | Voltage transfer characteristics of (a) an inverter and a NAND gate (b) an inverter and a NOR gate using CNT-FETs (11,9) with $V_{fb}=0$ V and $\varphi_0=0$ . The dimensions of both the n-type CNT-FET and p-type CNT-FET are: $T_{ox1}=15$ nm, $T_{ox2}=120$ nm and $L=250$ nm.                                                      | 43 |  |

| Figure 2.9:                                                                                                                                                                                                                                                                                   | Meyer capacitance model for CNT-FETs [114].                                                                                                                                                                                                                                                                                             | 44 |  |

| Figure 2.10:                                                                                                                                                                                                                                                                                  | The capacitances of CNT-FET (11,9) with $V_{fb}$ = -0.79 V and $\varphi_0$ = 0. The device dimensions are $T_{ox1}$ = 15 nm, $T_{ox2}$ = 120 nm and L = 250 nm. In modeled curve, $Q_{01}$ = $Q_{02}$ = 0.                                                                                                                              | 49 |  |

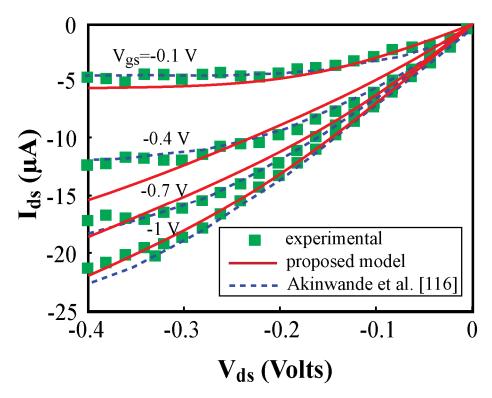

| Figure 2.11:                                                                                                                                                                                                                                                                                  | I-V characteristics for a self-aligned p-type CNT-FET with Ohmic metallic contacts shown by solid lines. The CNT-FET parameters are: $\kappa = 15$ , $t_{ox} = 8$ nm and $d = 1.7$ nm. Experimental data shown by rectangles is taken from the work of Javey et al. [49]. Dotted line plots are from the work of Akinwande et al. [116] | 51 |  |

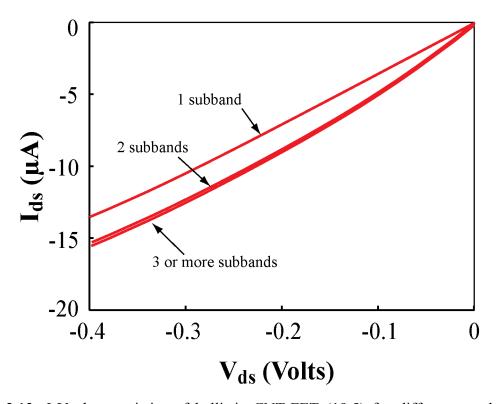

| Figure 2.12:                                                                                                                                                                                                                                                                                  | I-V characteristics of ballistic CNT-FET (19,5) for different numbers of sub-bands.                                                                                                                                                                                                                                                     | 52 |  |

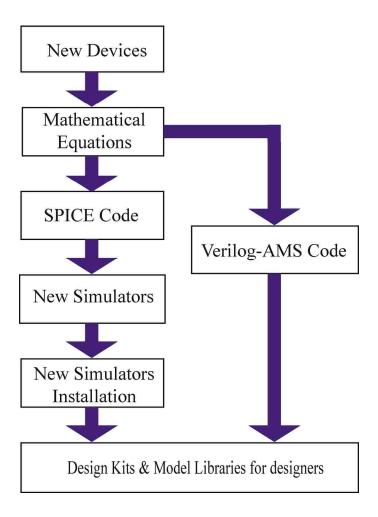

| Figure 2.13:                                                                                                                                                                                                                                                                                  | Steps to simulate a new device using Verilog-AMS code                                                                                                                                                                                                                                                                                   | 54 |  |

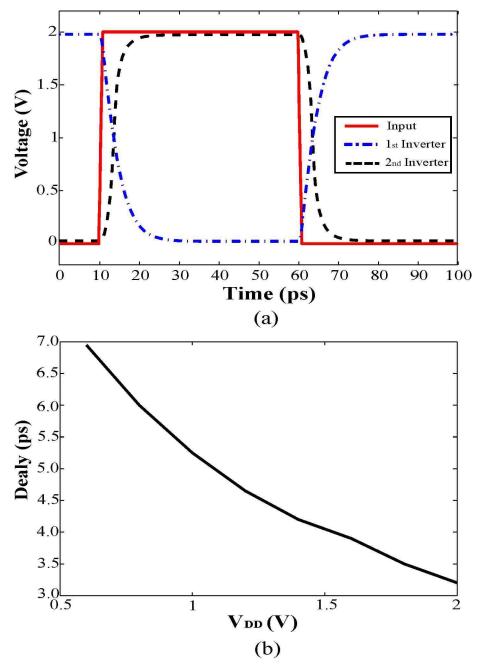

| Figure 2.14:                                                                                                                                                                                                                                                                                  | (a) Transient behavior of an inverter pair using CNT-FETs (11,9) with $V_{fb} = 0$ V and $\varphi_0 = 0$ . The dimensions of both the n-type CNT-FET and p-type CNT-FET are: $T_{ox1} = 15$ nm, $T_{ox2} = 120$ nm and $L = 250$ nm and (b) average delay of the inverter pair versus supply voltage.                                   | 55 |  |

| Figure 2.15:                                                                                                                                                                                                                                                                                  | (a) Schematic of a 5-stage ring oscillator, (b) output waveform, (c) the oscillating frequency versus supply voltage, $V_{DD}$ . The dimensions of both the n-type and p-type CNT-FETs are: $d = 2$ nm and $L = 600$ nm                                                                                                                 | 56 |  |

| Figure 2.16: | Oscillating frequency of the 5-stage ring oscillator versus length of the CNT-FETs.            | 57 |

|--------------|------------------------------------------------------------------------------------------------|----|

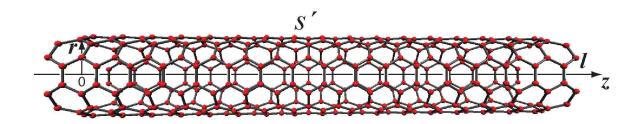

| Figure 3.1:  | Geometry of a single wall carbon nanotube (SWCNT).                                             | 63 |

| Figure 3.2:  | The equivalent circuit of a metallic SWCNT interconnect                                        | 74 |

| Figure 3.3:  | Equivalent circuit of a SWCNT contact.                                                         | 74 |

| Figure 3.4:  | $\mid Z_{in} \mid$ versus frequency for different lengths of SWCNTs                            | 76 |

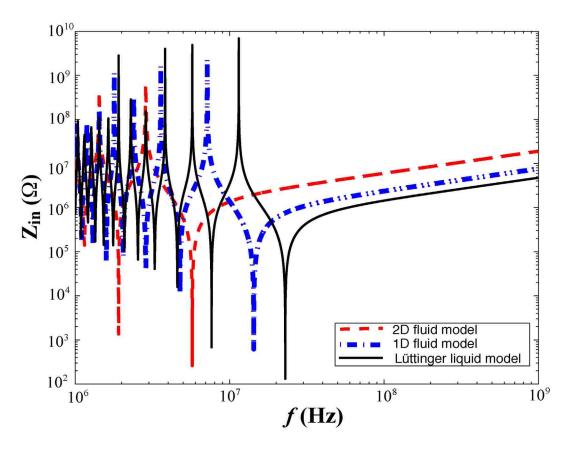

| Figure 3.5:  | $\mid Z_{in} \mid$ versus frequency using different model for a 10 $\mu m$ length SWCNT.       | 77 |

| Figure 3.6:  | Schematic of a 2-port network of interconnects                                                 | 79 |

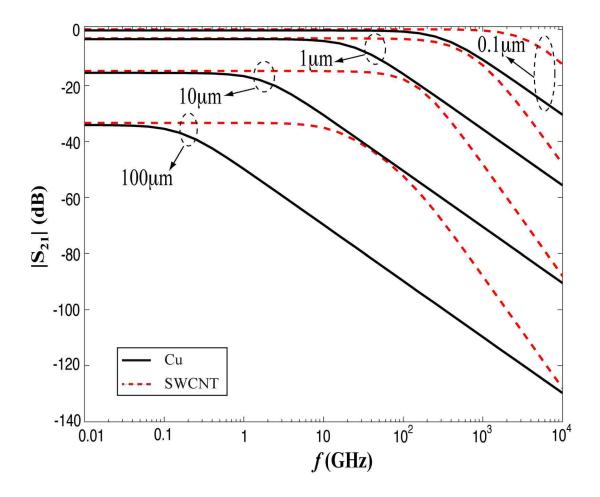

| Figure 3.7:  | S <sub>21</sub> (amplitude) versus frequency for different lengths SWCNT and Cu interconnects. | 81 |

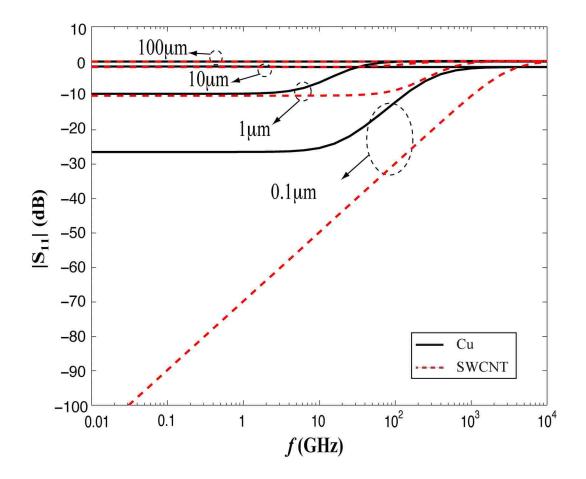

| Figure 3.8:  | S <sub>11</sub> (amplitude) versus frequency for different lengths SWCNT and Cu interconnects. | 82 |

| Figure 3.9:  | $S_{21}$ (amplitude) versus frequency using different model for a 1 $\mu m$ length SWCNT.      | 83 |

| Figure 3.10: | S <sub>11</sub> (amplitude) versus frequency using different model for a 1 μm length SWCNT.    | 84 |

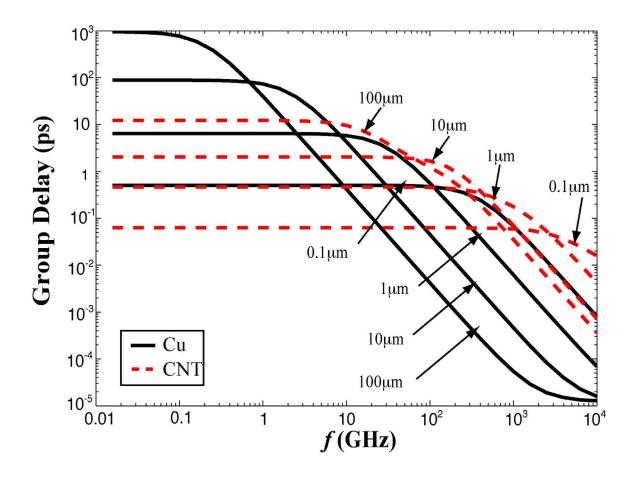

| Figure 3.11: | Group delay versus frequency for different lengths SWCNT and Cu interconnects.                 | 87 |

| Figure 4.1:  | Equivalent circuit of a metallic MWCNT interconnect.                                           | 92 |

| Figure 4.2:  | Simplified equivalent circuit of a metallic MWCNT interconnect.                                | 92 |

| Figure 4.3:  | Simple equivalent circuit model of a metallic MWCNT interconnect.                              | 92 |

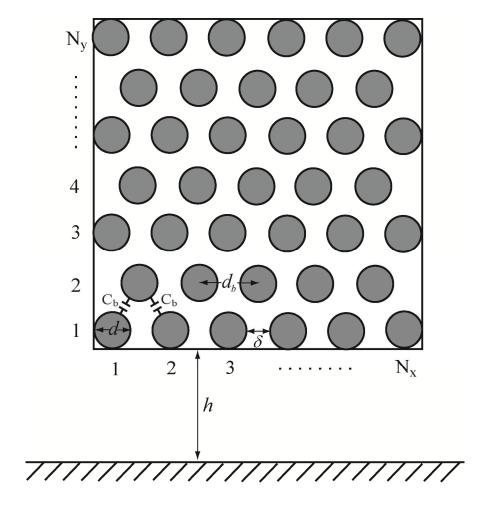

| Figure 4.4:  | Cross-section of a SWCNT bundle interconnect.                                                  | 94 |

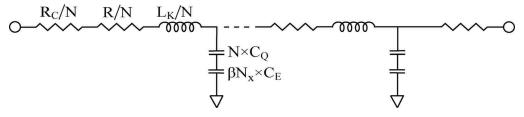

| Figure 4.5:  | Equivalent circuit of a SWCNT bundle interconnect                                              | 97 |

| Figure 4.6:  | Simplified equivalent circuit of a SWCNT bundle                                                | 07 |

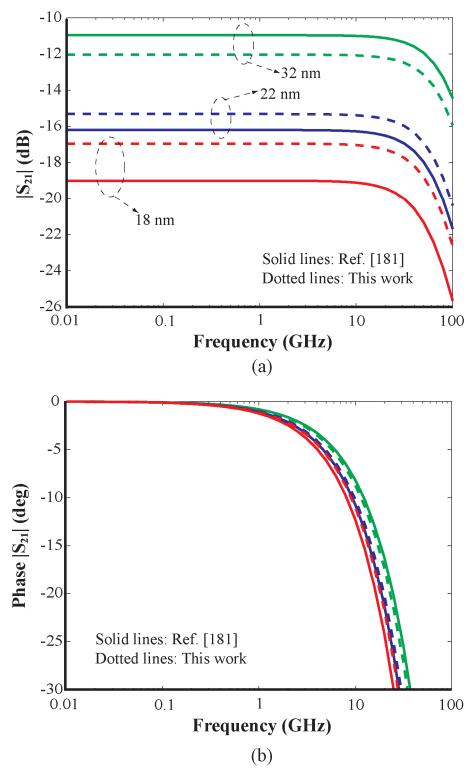

| Figure 4.7: Comparison of S <sub>21</sub> from our model and Li et al. model [181] for MWCNT interconnects: (a) amplitude and (b) phase. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

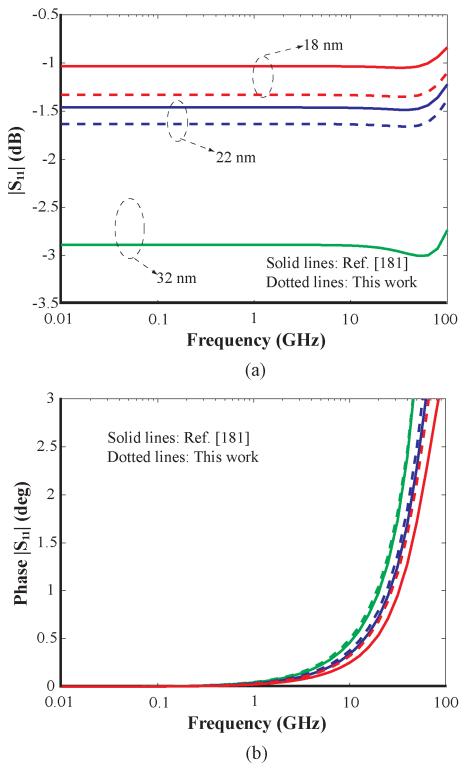

| Figure 4.8:                                                                                                                              | Comparison of S <sub>11</sub> from our model and Li et al. model [181] for MWCNT interconnects: (a) amplitude and (b) phase.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |  |  |

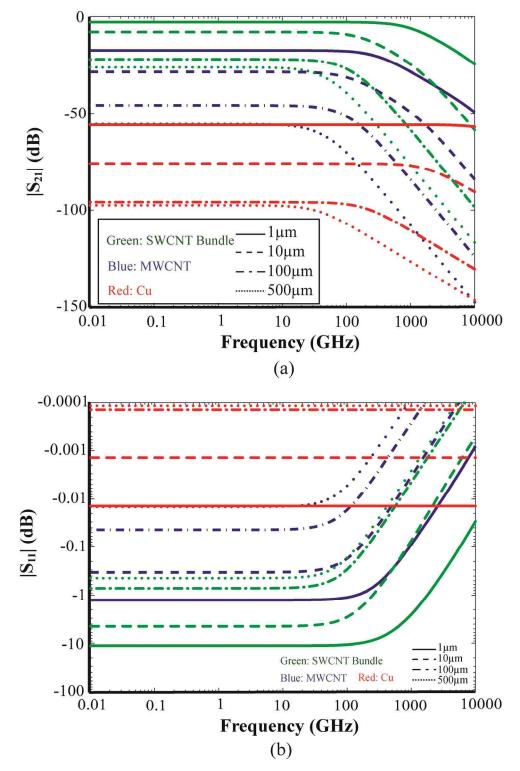

| Figure 4.9:                                                                                                                              | Calculated S-parameters of different interconnects: (a) $S_{21}$ (amplitude) and (b) $S_{11}$ (amplitude).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 104 |  |  |

| Figure 4.10:                                                                                                                             | Inverter pair with interconnects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 106 |  |  |

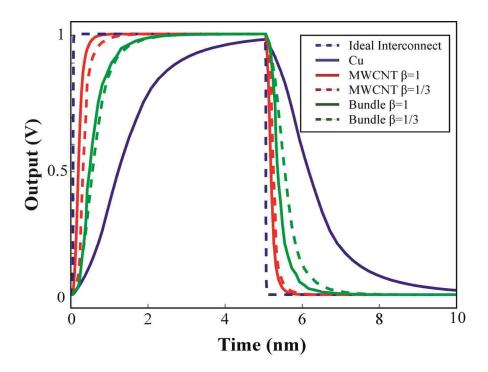

| Figure 4.11:                                                                                                                             | Output waveforms of an inverter pair with 10 µm length of different interconnect wires.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 107 |  |  |

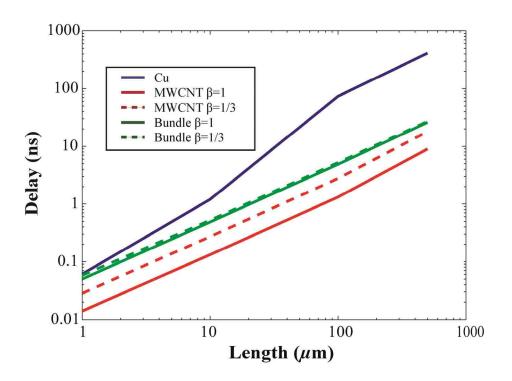

| Figure 4.12:                                                                                                                             | Propagation delays of interconnects of different lengths for 22 nm technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 108 |  |  |

| Figure 5.1:                                                                                                                              | $\pi$ model of an on-chip inductor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 113 |  |  |

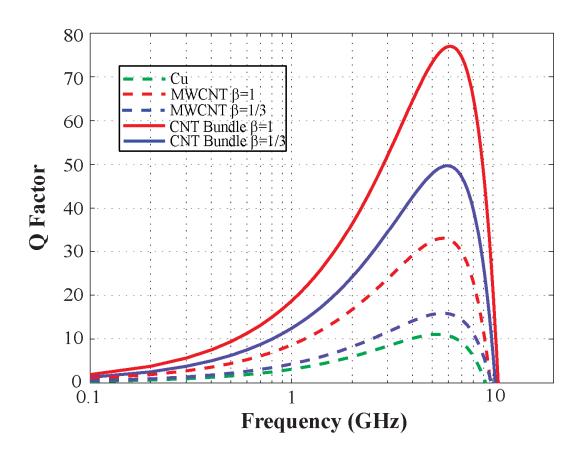

| Figure 5.2:                                                                                                                              | Q-factor of inductors based on CNT and Cu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 115 |  |  |

| Figure 5.3:                                                                                                                              | (a) Circuit diagram of a CMOS cross-coupled LC VCO, (b) equivalent circuit of LC VCO and (c) circuit to estimate the negative resistance of the cross-coupled pair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 117 |  |  |

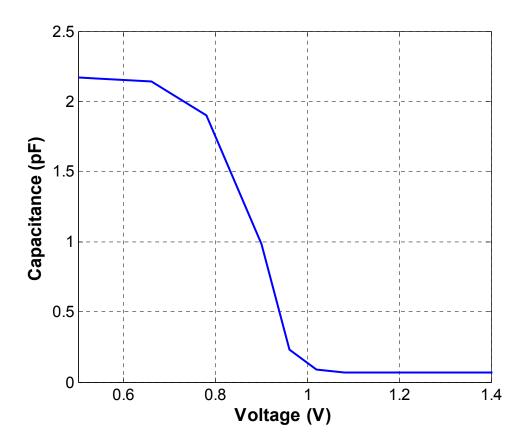

| Figure 5.4:                                                                                                                              | C-V curve of a varactor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 118 |  |  |

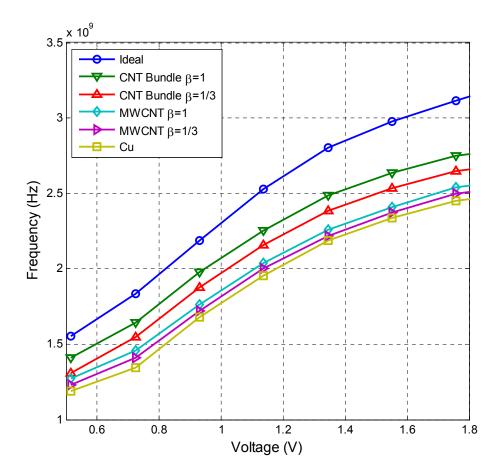

| Figure 5.5:                                                                                                                              | VCO oscillation frequency versus control voltage with difference inductors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 120 |  |  |

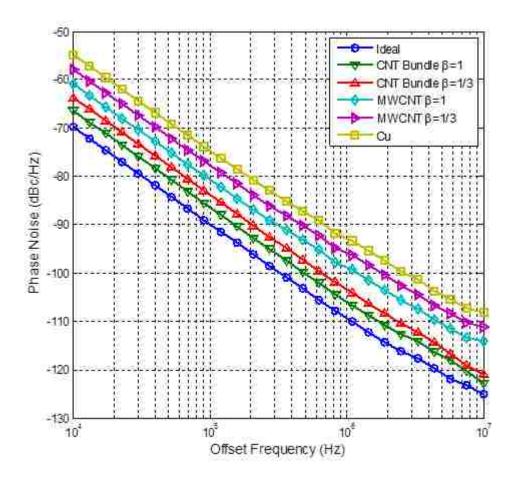

| Figure 5.6:                                                                                                                              | VCO phase noise versus offset frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 121 |  |  |

| Figure 6.1:                                                                                                                              | (a) CMOS circuit of 2N-2N2P XNOR/XOR gate and (b) timing for 2N-2N2P XNOR/XOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 125 |  |  |

| Figure 6.2:                                                                                                                              | (a) Quasi-static energy recovery logic (QSERL), (b) Complementary clocked power supplies, (c) CMOS circuit of QSERL XNOR/XOR gate and (d) separated QSERL XNOR and XOR gates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 127 |  |  |

| Figure 6.3:                                                                                                                              | (a) CMOS circuit of CAL XNOR/XOR gate and (b) idealized CAL timing waveforms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 129 |  |  |

| Figure 6.4:                                                                                                                              | (a) CMOS circuit of new CAL XNOR/XOR gate and (b) ideal new CAL input waveforms. Note: $XOR(O/P) = \frac{1}{4} \frac{1}{12} 1$ | 120 |  |  |

|                                                                                                                                          | $A \overline{B} + \overline{A} B$ and $XNOR(O/P) = AB + \overline{A} \overline{B}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 130 |  |  |

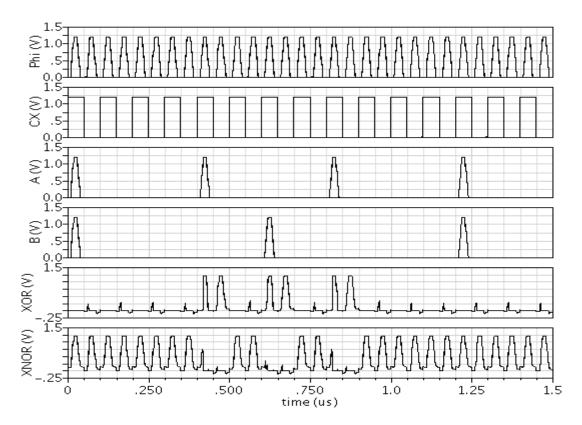

| Figure 6.5:  | Simulated New CAL waveforms.                                                                                                                 | 132 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

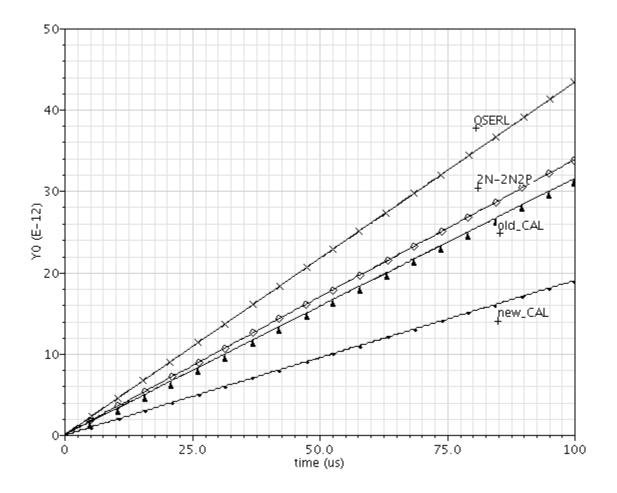

| Figure 6.6:  | Simulated energy dissipation of different ERL XNOR/XOR gates.                                                                                | 133 |

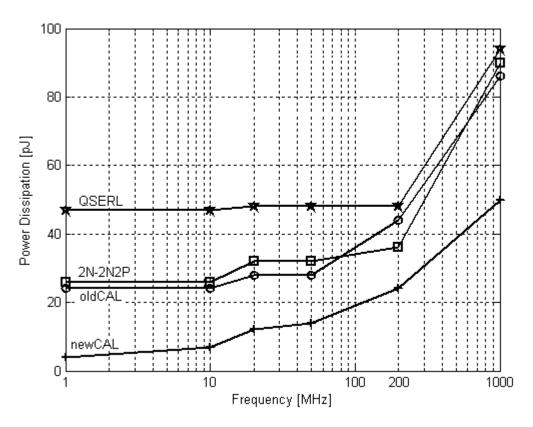

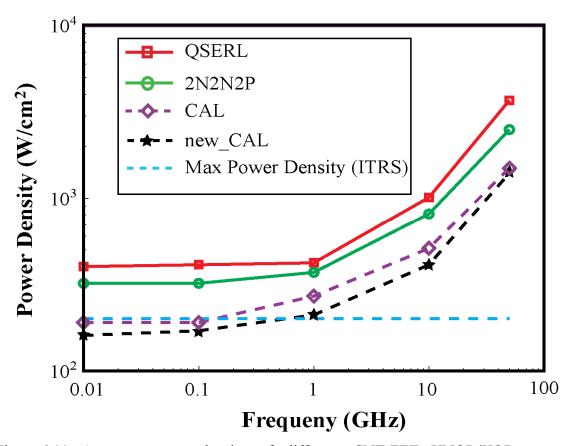

| Figure 6.7:  | Simulated power dissipation versus frequency.                                                                                                | 134 |

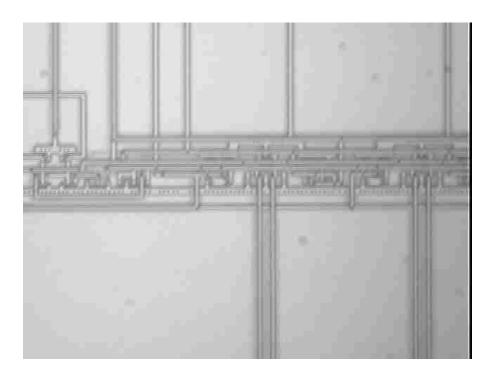

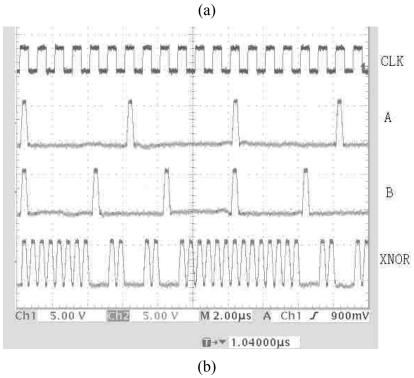

| Figure 6.8:  | (a) Microphotograph of CAL XNOR/XOR gates and (b) experimental results.                                                                      | 136 |

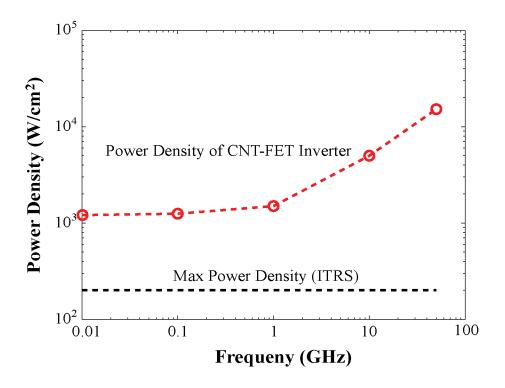

| Figure 6.9:  | Average power density for a CNT-FET inverter. Note: The plot is obtained from Verilog-AMS in Cadence/Spectre.                                | 137 |

| Figure 6.10: | CNT-FET New CAL XNOR/XOR. Note: XOR(O/P) = $A \overline{B} + \overline{A} B$ and XNOR(O/P) = $AB + \overline{A} \overline{B}$                | 138 |

| Figure 6.11: | Average power density of different CNT-FET XNOR/XOR energy recovery circuits                                                                 | 139 |

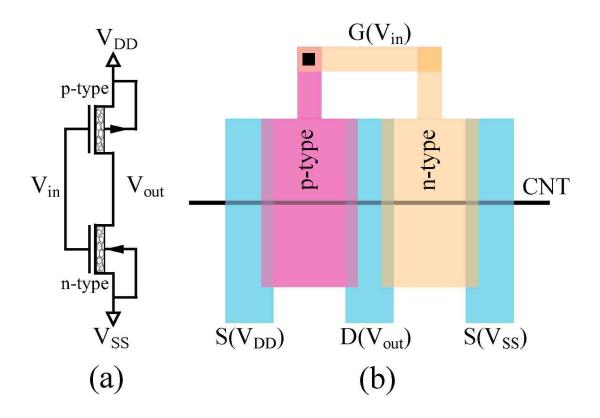

| Figure 7.1:  | (a) CNT-FET inverter and (b) of CNT-FET inverter layout [44].                                                                                | 142 |

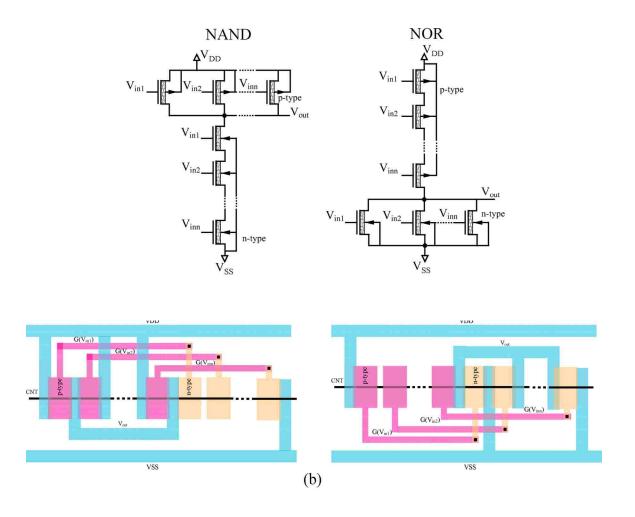

| Figure 7.2:  | (a) CNT-FET NAND and NOR gates and (b) of CNT-FET NAND and NOR gates layouts                                                                 | 143 |

| Figure 7.3:  | (a) Physical layout showing shorts in a CNT-FET NAND gate with stuck-at faults (dotted lines) and (b) open faults shown by X in the circuit. | 145 |

| Figure 7.4:  | Transient simulations of a 2-input CNT-FET NAND gate with and without stuck-at faults.                                                       | 147 |

| Figure 7.5:  | Transient simulations of a 2-input CNT-FET NAND gate with and without stuck-open faults                                                      | 148 |

| Figure B.1:  | Transient behavior of an inverter pair inter-connected by 100µm CNT wire length before and after SOCl <sub>2</sub> adsorption.               | 181 |

| Figure B.2:  | RO frequency dependence on supply voltage, $V_{DD}$ . The dimensions of both the n-type and p-type CNT-FETs are: $d=2\ nm$ and $L=600\ nm$ . | 181 |

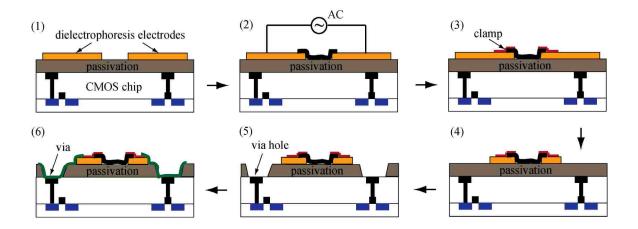

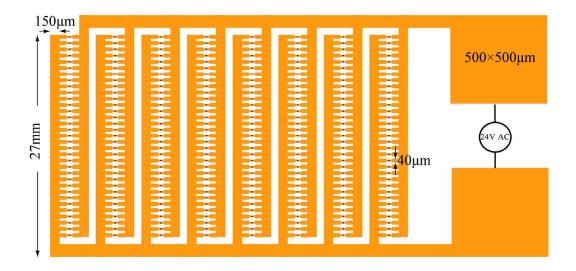

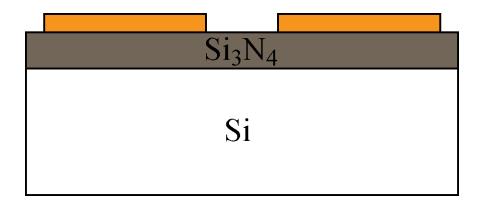

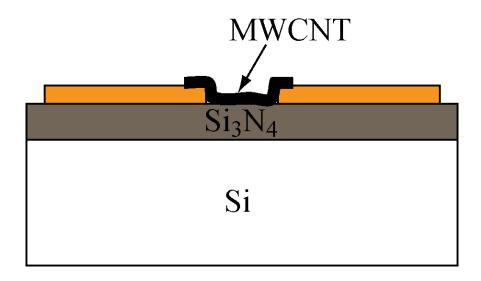

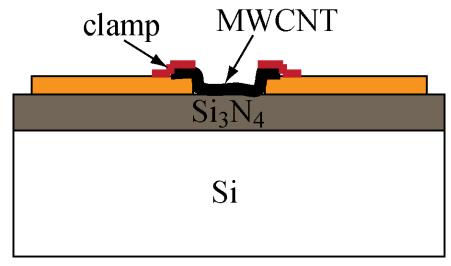

| Figure C.1:  | Process flow to assemble an array of MWCNT interconnects on top of a platform CMOS chip [200]                                                | 183 |

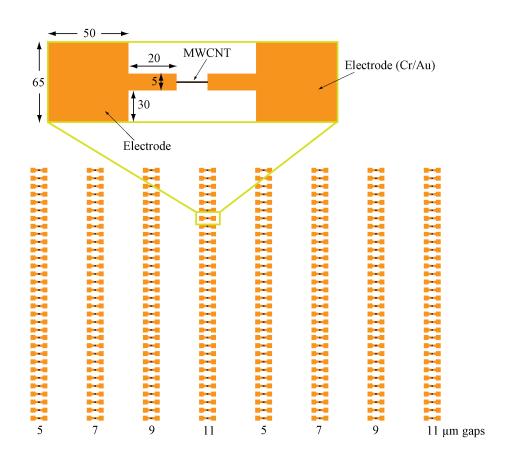

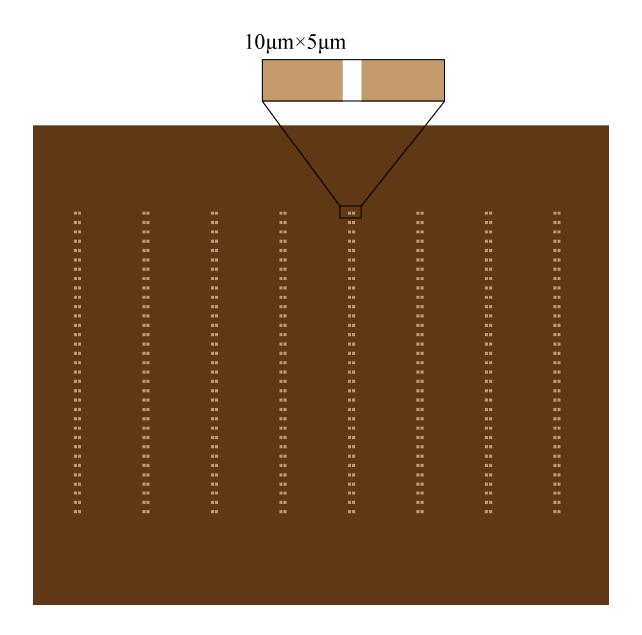

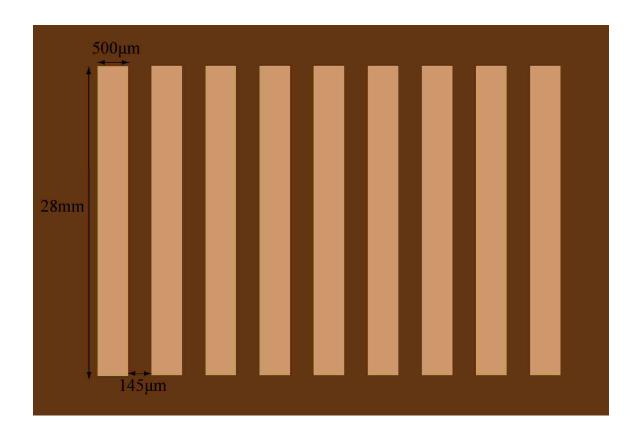

| Figure C.2: | Top-view of MWCNT interconnects between electrodes (unit: μm).                     | 183 |

|-------------|------------------------------------------------------------------------------------|-----|

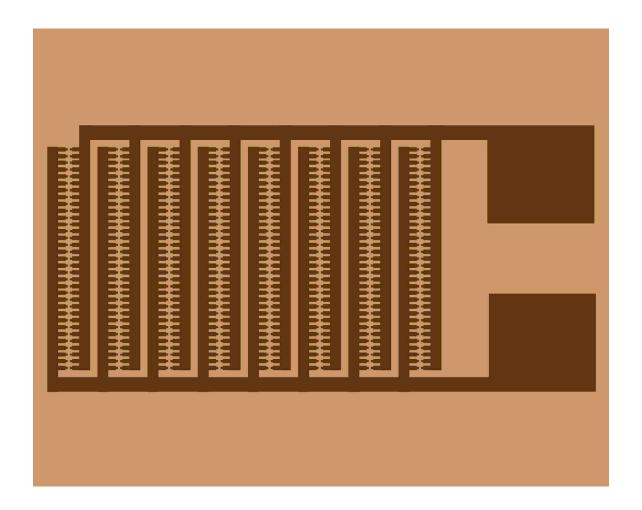

| Figure C.3: | Top-view of the mask for first lithography step                                    | 185 |